Functionally Reduced And-Inverter Graph (FRAIG)

Personal Project @ EE3011 Data Structure and Programming

Personal Project @ EE3011

Data Structure and Programming

Implemente a special circuit

representation with simplification.

Figure 1. 9th place out of 170+ students.

In this final project, we are going to implement a special circuit representation, FRAIG, from a circuit description file and we need to implement circuit simplification techniques to reduce the whole circuit architecture. This project is sponsored by Cadence Design Systems and I got the 9th place out of 170+ students, as shown above on Figure 1.

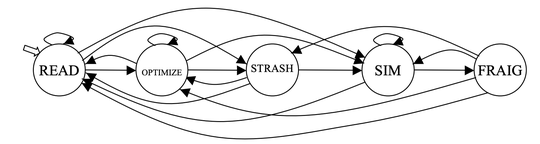

Figure 2. Processing flow overview.

The program performs the following processes to simplfy the circuits as shown above on Figure 2.

- Read:Parse a description file in the AIGER format and sweep out the gates that cannot be reached from primary outputs.

- Optimize:Perform optimizations without altering the functionality, replacing an always-inverse fan-ins AND gate by zero.

- Strash:Use structural hash to merge the structurally equivalent signals by comparing gate types and permuting inputs.

- Sim:Simulate boolean logic to group potentially equivalent gates into functionally equivalent candidate (FEC) pair.

- Fraig:Use a boolean satisfiability (SAT) solver to formally prove or disprove FEC pair and merge equivalent gates.

For more information, please refer to our report and our code is also publically available on GitHub.